# **ALBERT WANG**

# PRACTICAL ESD PROTECTION DESIGN

# **Practical ESD Protection Design**

#### **Table of Contents**

#### **Chapter 1: Why ESD?**

§1.1 A Historical Perspective

§1.2 ESD and The Dangers

§1.3 ESD Protection: The Principles

§1.4 ESD Protection: More or Less?

§1.5 ESD Protection: Evolution to Revolution References

#### **Chapter 2: ESD Failure Analysis**

§2.1 ESD Failures Analysis

§2.1.1 ESD Failure Criteria

§2.1.2 Hard and Soft ESD Failures

§2.2 ESD FA Techniques

§2.3 ESD Failure Signatures

§2.4 ESD Soft Failures

§2.5 ESD Failure Correlation

§2.6 ESD Failure Models

References

#### **Chapter 3: ESD Test Models and Standards**

§3.1 ESD Origins

§3.2 HBM Model

§3.3 MM Model

§3.4 CDM Model

§3.5 IEC Model

§3.6 TLP Model

§3.7 Summary

References

### **Chapter 4: ESD Protection Devices**

```

§4.1 On-Chip ESD Protection Mechanisms

§4.1.1 Switch for ESD Discharge

§4.1.2 ESD Protection: Active vs. Passive

§4.2 Diode for ESD Protection

§4.2.1 Diode Device Physics

§4.2.2 Diode in ESD Protection

§4.2.3 Diode ESD Parasitic Modelling

§4.3 BJT for ESD Protection

§4.3.1 BJT Device Physics

§4.3.2 BJT in ESD Protection

§4.3.3 BJT ESD Parasitic Modelling

§4.4 MOSFET for ESD Protection

§4.4.1 MOSFET Device Physics

§4.4.2 ggMOS in ESD Protection

§4.4.3 MOSFET ESD Parasitic Modelling

§4.5 SCR for ESD Protection

§4.5.1 SCR Device Physics

§4.5.2 SCR in ESD Protection

§4.5.3 SCR ESD Parasitic Modelling

§4.6 Summary

References

```

#### **Chapter 5: ESD Protection Circuits**

§5.1 I/O ESD Protection §5.1.1 Two-Stage ESD Protection §5.1.2 Multiple-Fingers ESD Protection **§5.1.3 MOSFET ESD Protection Circuits** §5.1.4 BJT ESD Protection Circuits §5.1.5 SCR ESD Protection Circuits §5.2 ESD Self-Protection §5.2.1 Output ESD Protection §5.2.2 ESD Self-Protection §5.3 Low-Triggering ESD Protection Circuits §5.4 ESD Power Clamps §5.4.1 Diode-String Power Clamps §5.4.2 MOSFET Power Clamps §5.4.3 SCR Power Clamps §5.4.4 Any Switch Power Clamps §5.5 Summary References

#### **Chapter 6: Full-Chip ESD Protection**

§6.1 Full-Chip ESD Protection Principles

§6.2 ESD Protection Design Window

§6.3 Advanced ESD Protection: More at Less

§6.3.1 Dual-Polarity ESD Protection

§6.3.2 Multiple-Polarity ESD Protection

§6.4 Full-Chip ESD Protection Schemes

§6.4.1 Full-Chip ESD Consideration

§6.4.2 Pad-Clamp Scheme

§6.4.3 Global ESD Bus Scheme

§6.5 No Universal ESD Protection Solution

#### **Chapter 7: Mixed-Signal & Hi-V ESD Protection**

§7.1 ESD Protection for Mixed-Signal ICs

§7.2 ESD Protection for Multiple-Voltages ICs

§7.3 ESD Protection for High-Voltage ICs

§7.3.1 ESD Design Window Compliance

§7.3.2 Latch-up Immunity

§7.4 Summary

References

#### **Chapter 8: TCAD-Based Mixed-Mode ESD Designs**

§8.1 ESD Design Optimization and Prediction

§8.2 TCAD-Based Mixed-Mode ESD Simulation-Design Methodology

§8.3 Mixed-Mode ESD Simulation-Design Examples

§8.3.1 Example 1: Understand TCAD ESD Simulation

§8.3.2 Example-2: ggNMOS *vs.* gcNMOS ESD Protection

§8.3.3 Example-3: ESD Power Clamp in 0.35µm CMOS

§8.3.4 Example-4: Optimize HV ESD Protection Design

§8.3.5 Example-5: ESD Layout Analysis by 3D TCAD

§8.3.6 Example-6: Multi-Stimuli TCAD ESD Simulation

§8.4 Summary

References

#### **Chapter 9: RF ESD Protection**

§9.1 What's Special for RF ESD Protection?

§9.2 RF ESD Protection Characterization

§9.3 Low-Parasitic ESD Protection Solutions

§9.4 RF ESD Protection Design Example

§9.5 Summary

References

#### Chapter 10: ESD-RFIC co-Design

§10.1 ESD-IC Interactions §10.1.1 IC Affects ESD Protection §10.1.2 ESD Affects IC Performance §10.2 ESD-RFIC Co-Design §10.2.1 ESD-RFIC Co-Design Principle §10.2.2 ESD-RFIC Co-Design Examples §10.3 Summary Reference

#### **Chapter 11: ESD Layout Designs**

§11.1 Layout is Critical to ESD Protection

§11.2 Basic ESD Protection Layout

§11.3 Advanced ESD Protection Layout

§11.3.1 Advanced ESD Layout Considerations

§11.3.2 ESD Design Layout is an Art

§11.4 3D TCAD for ESD Layout Designs

§11.5 Summary

References

### Chapter 12: ESD vs. IC Technologies

§12.1 IC Technologies and ESD Protection

§12.1.1 ESD Metal Interconnects

§12.1.2 Technology-ESD Co-Development

§12.1.3 Graphene Heat Spreading

§12.2 Technology Affects ESD Design Window

§12.3 Lowering ESD Protection for Advanced ICs?

§12.4 Summary

References

#### **Chapter 13: ESD Circuit Simulation by SPICE**

§13.1 ESD Device Behavior Modeling

§13.2 Full-Chip ESD Circuit Simulation by SPICE

§13.2.1 Principle for ESD Circuit Simulation by SPICE

§13.2.2 Circuit-Level ESD Design Verification by SPICE

§13.3 Summary

Reference

#### **Chapter 14: Emerging ESD Protection**

§14.1 Emerging ESD Protection Challenges

§14.2 Dispensable ESD Protection

§14.3 Field-Programmable ESD Protection

§14.3.1 Nano-Crystal Quantum-Dots ESD Protection

§14.3.2 SONOS ESD Protection

§14.4 Interposer/TSV-Based ESD Protection

§14.5 Summary

Reference

#### **Chapter 15: ESD CAD for Full-Chip Design Verification**

§15.1 Full-Chip ESD Design Verification§15.2 CAD Algorithm for ESD Design Verification§15.3 Full-Chip ESD Design Verification Examples§15.4 SummaryReference

## **Chapter 16: New CDM ESD Protection**

§16.1 Misconception in CDM ESD Protection§16.2 Analyzing Pad-Based CDM ESD Protection§16.3 Internally-Distributed CDM ESD Protection§16.4 SummaryReference

### **Chapter 17: Future ESD Protection Outlook**

§17.1 The Fundamental ESD Protection Problem

§17.2 Above-IC Nano Crossbar Array ESD Switch

§17.3 Graphene ESD Protection Switch

§17.4 Graphene ESD Protection Interconnects

§17.5 Future ESD Protection Outlook

§17.6 Summary

References

# An authoritative single-volume reference on the design and analysis of ESD protection for ICs

Electrostatic discharge (ESD) is a major reliability challenge to semiconductors, integrated circuits (ICs), and microelectronic systems. On-chip ESD protection is a vital to any electronic products, such as smartphones, laptops, tablets, and other electronic devices. Practical ESD Protection Design provides comprehensive and systematic guidance on all major aspects of designs of on-chip ESD protection for integrated circuits (ICs).

Written for students and practicing engineers alike, this one-stop resource covers essential theories, hands-on design skills, computer-aided design (CAD) methods, characterization and analysis techniques, and more on ESD protection designs. Detailed chapters examine an array of topics ranging from fundamental to advanced, including ESD phenomena, ESD failure analysis, ESD testing models, ESD protection devices and circuits, ESD design layout and technology effects, ESD design flows and co-design methods, ESD modelling and CAD techniques, and future ESD protection concepts. Based on the author's decades of design, research and teaching experiences, Practical ESD Protection Design:

- Features numerous real-world ESD protection design examples

- Emphasizes on ESD protection design techniques and procedures

- Describes ESD-IC co-design methodology for high-performance mixed-signal ICs and broadband radio-frequency (RF) ICs

- Discusses CAD-based ESD protection design optimization and prediction using both Technology and Electrical Computer-Aided Design (TCAD/ECAD) simulation

- Addresses new ESD CAD algorithms and tools for full-chip ESD physical design verification

- Explores the disruptive future outlook of ESD protection

*Practical ESD Protection Design* is a valuable reference for industrial engineers and academic researchers in the field, and an excellent textbook for electronic engineering courses in semiconductor microelectronics and integrated circuit designs.

**Albert Wang, PhD,** is a Professor in the Department of Electrical and Computer Engineering at the University of California, Riverside, USA. He was an IC designer in the Silicon Valley before joining the academia. His research resulted in two books, more than 300 peer-reviewed papers, and 16 granted U.S. patents. He was the President of IEEE Electron Devices Society. He is a Fellow of the National Academy of Inventors and a Fellow of IEEE.

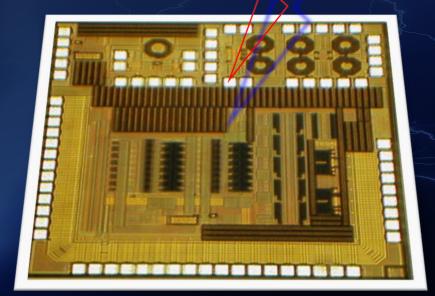

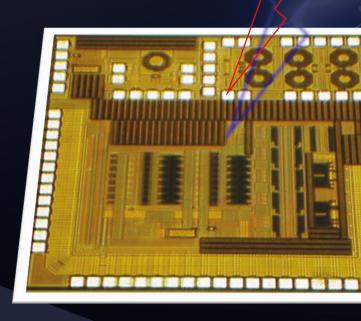

Cover Design: Wiley Cover Image: © Albert Wang

WILEY

www.wiley.com

IEEE PRESS

WANG

## **ALBERT WANG**

# PRACTICAL ESD PROTECTION DESIGN

WILEY

IEEE PRESS